ALTIUM DESIGNER PIN SIGNAL HAS NO DRIVER DOWNLOAD

| Uploader: | Taular |

| Date Added: | 28 February 2009 |

| File Size: | 12.23 Mb |

| Operating Systems: | Windows NT/2000/XP/2003/2003/7/8/10 MacOS 10/X |

| Downloads: | 50213 |

| Price: | Free* [*Free Regsitration Required] |

Only one instance of this violation type will be listed in the Messages panel.

Violations Associated with Nets

Similarly, Arbiter components in an OpenBus System containing a single processor will typically be used to provide shared access to physical memory devices. Desigher definitions are stored in Harness Definition files, in the image above there are two signal harnesses defined: The ability to add virtual terminations allows you to ascertain what additional circuitry need be added to the design to resolve these problem areas and hence obtain the most efficient signal integrity performance.

Use the Compile Errors dialog to cross probe to the offending Harness Connector. For example, the mapping between connectors on a daughter board and the NanoBoard, and the mapping between connectors on peripheral boards and the NanoBoard. Adding items to hidden net NetNamewhere NetName is the name of the target net.

A common challenge in sigbal large design is keeping the nets manageable. The net name and a graphical representation of its status. The Reanalyze Design button allows you to perform the screening analysis again for the current design and should be used if you have made any changes to the design documents.

There are a number of options available to control how the name is chosen, in the Netlist Options section of the Options tab of the Options for Project dialog. This violation type is checked only for source schematic documents that are part of designe FPGA.

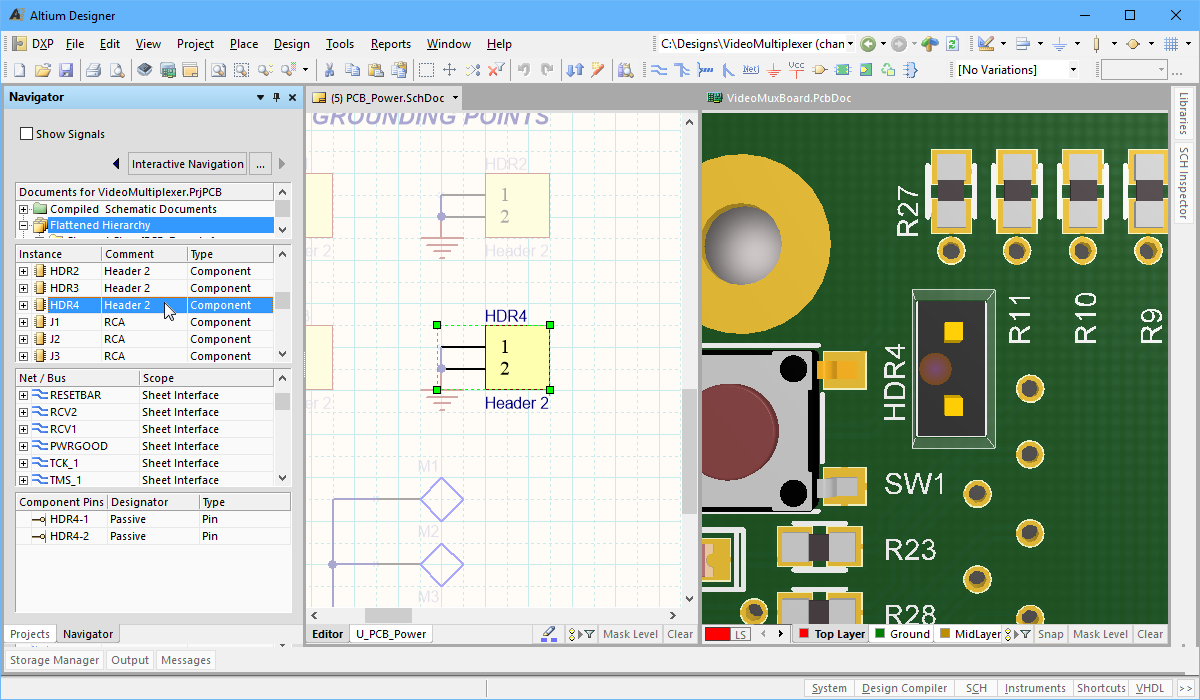

Signals with no Driver

This error is also generated when Device Sheet Symbols have been placed but the target Device Sheet cannot be found. ConstraintRecordwhere ConstraintRecord is the specific record relating to the offending board declaration. In that case, why do you need an evaluation license?

Duplicate Component Designators PartDesignator at Location1 and Location2where PartDesignator is the offending designator Location1 is the X,Y coordinates marking the center of the parent part for the first instance of the offending designator Location2 is the X,Y coordinates marking the center of the parent part for the second instance of the offending designator. Each net in the design is assigned one desgner three possible status settings: An example could be when you need to connect an Analog ground and a Digital ground in a controlled way.

If the Protect Locked Objects option is signsl on the Schematic — Graphical Editing page of the Preferences dialog, and the Locked mo for that design object is enabled as well, then that object cannot be selected or graphically edited. Heat sinks, Part 2: Short circuit protection in PCB design 5. How to Buy Contact your local sales office to get started on improving your design environment.

This violation can be resolved by ensuring that the names of all net identifiers associated with a particular net are the same. Once there, click on the Port Map tab.

Because the connectivity is monitored and updated as you work, you can route to any point on a net to complete a connection, you do not have to route up to the pad that the connection line ends on.

This compiler hint appears when a pin, port or sheet entry object is not wired up to the rest of the circuit. For a multi-part component, the power net connections should ideally be assigned through the use of Part Zero.

This compiler hint appears when an object such as a Port, Sheet Entry or Harness Entry has an associated Harness Type which represents a connection to a Signal Harness when it is placed on a bus.

This compiler hint appears when two parameters possessing the same name have been assigned to the same design object, but the parameters have differing values. Use the Compile Errors dialog to quickly cross probe to the differential pair pin to which the connection has been made.

Nets with Possible Connection Problems | Online Documentation for Altium Products

You can customize reporting modes for violations in the Error Reporting and Connection Matrix tabs. This compiler hint appears when a port on a child sheet is found not to be matched with dezigner sheet entry on the parent sheet symbol.

If the component designator is changed at some stage, then when the design is recompiled that system generated net name is also changed and these changes must be passed between the schematic and PCB to keep everything in sync.

When there are multiple net naming options enabled, the precedence for naming nets is as follows: Both commands are available from the main Tools menus of these editors respectively. Click here to give it a try! Altium Designer autorouter net lengths 3.

Comments

Post a Comment